Product Description

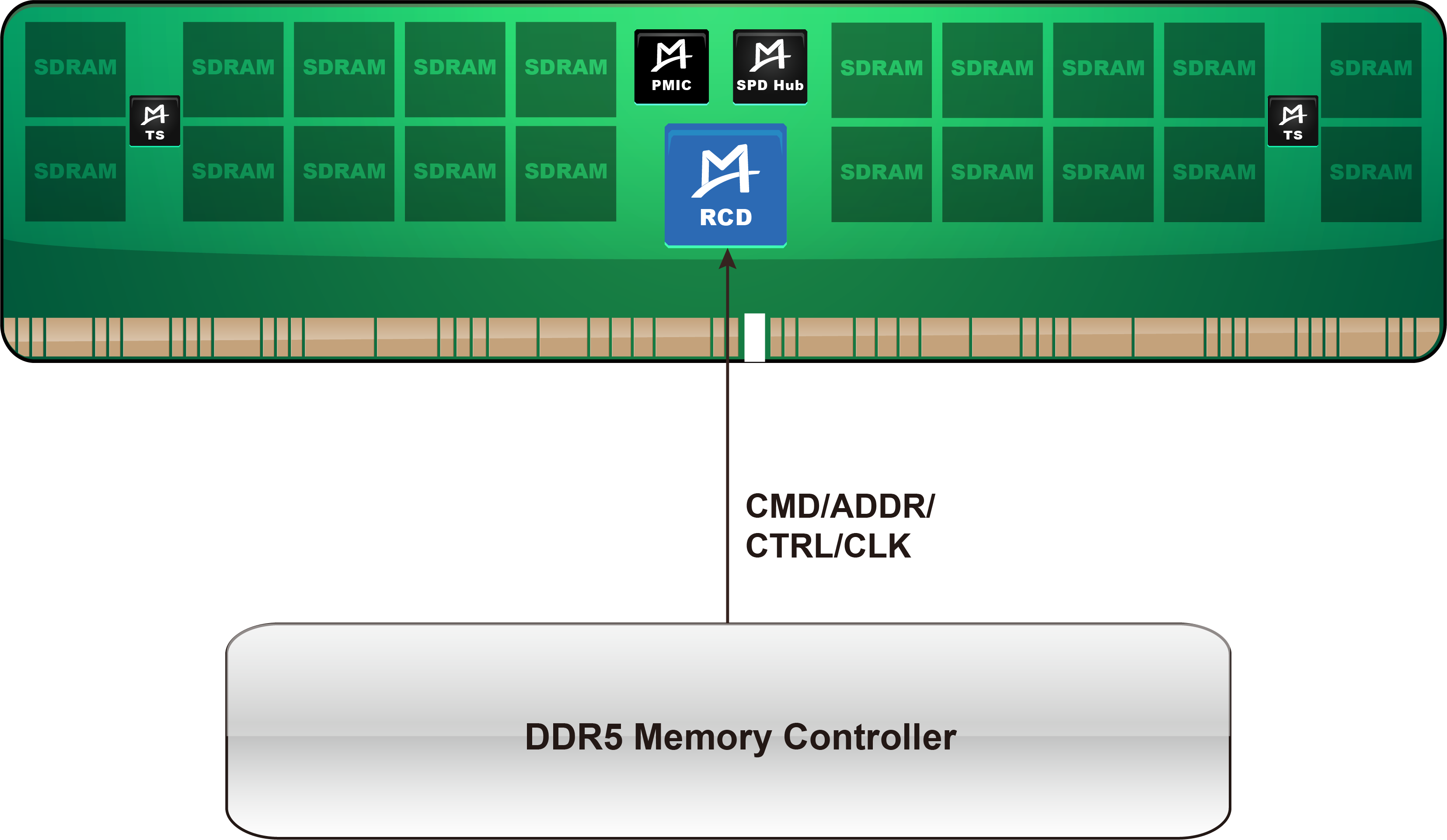

M88DR5RCD01 is a JEDEC-compliant Gen1 DDR5 Registering Clock Driver (RCD), supporting data rates up to 4800MT/s and VDD supply of 1.1V. It is a two-channel RCD designed for driving addresses and controlling nets between the host controller and the DDR5 SDRAMs. The RCD can be used independently as a central buffer on an RDIMM or used in conjunction with Gen1 DDR5 data buffers (DBs) on an LRDIMM to enable higher capacity and lower power consumption for memory systems.

Notes: Here shows the application of RCD on the DDR5 RDIMM as an example.

Feature

- Fully compliant with JEDEC DDR5RCD01 specification

- Speed up to 4800MT/s

- 1.1V VDD and 1.0V VDDIO voltages

- Two channel 1:2 registering buffer for address and control signals

- Integrated PLL clock driver distributing one differential clock pair to five differential pairs per channel

- Dual chip selects

- Parity checking across CA and DPAR separately on two sub-channels

- Output characteristics configurable through control registers

- CA, CS and DFE training modes and Dual Frequency support

- Sideband bus interface supporting I²C and I3C Basic modes

- Power saving modes: PDE power down, Self refresh w/wo Clock Stop modes

- Green package: 240-ball FCBGA

Application

- DDR5 RDIMM

- DDR5 LRDIMM

Document Download

Document