M88DDR4DB01是一款带差分选通信号的双4位双向Gen1 DDR4数据缓冲器(DB)芯片,用于DDR4 LRDIMM内存模组。该芯片符合JEDEC DDR4DB01标准,最高支持速率DDR4-2400,支持1.2V VDD电压。该芯片内置一个双4位总线接口,用以连接内存控制器;一个双4位DRAM接口,可连接两个4位DRAM芯片;以及一个输入控制总线接口,用以连接DDR4寄存缓冲器(RCD)芯片。

M88DDR4DB01的所有数据输入均采用伪差分模式,内置电压参考电路。而芯片的所有数据输出脚均端接上拉电源(VDD),经优化可驱动DDR4 LRDIMM板上单端或双端终接负载的数据线路。此外,用于采样数据输入的差分数据控制信号(DQS)可在芯片内部重新生成,以驱动与芯片相连的内存芯片的数据输出。

M88DDR4DB01的输入控制信号BCOM[3:0]、BCKE和BODT由一对时钟输入CK_t 与BCK_c进行采样。同时,该芯片还提供专用的ZQ校准引脚以及奇偶校验和顺序错误指示引脚。

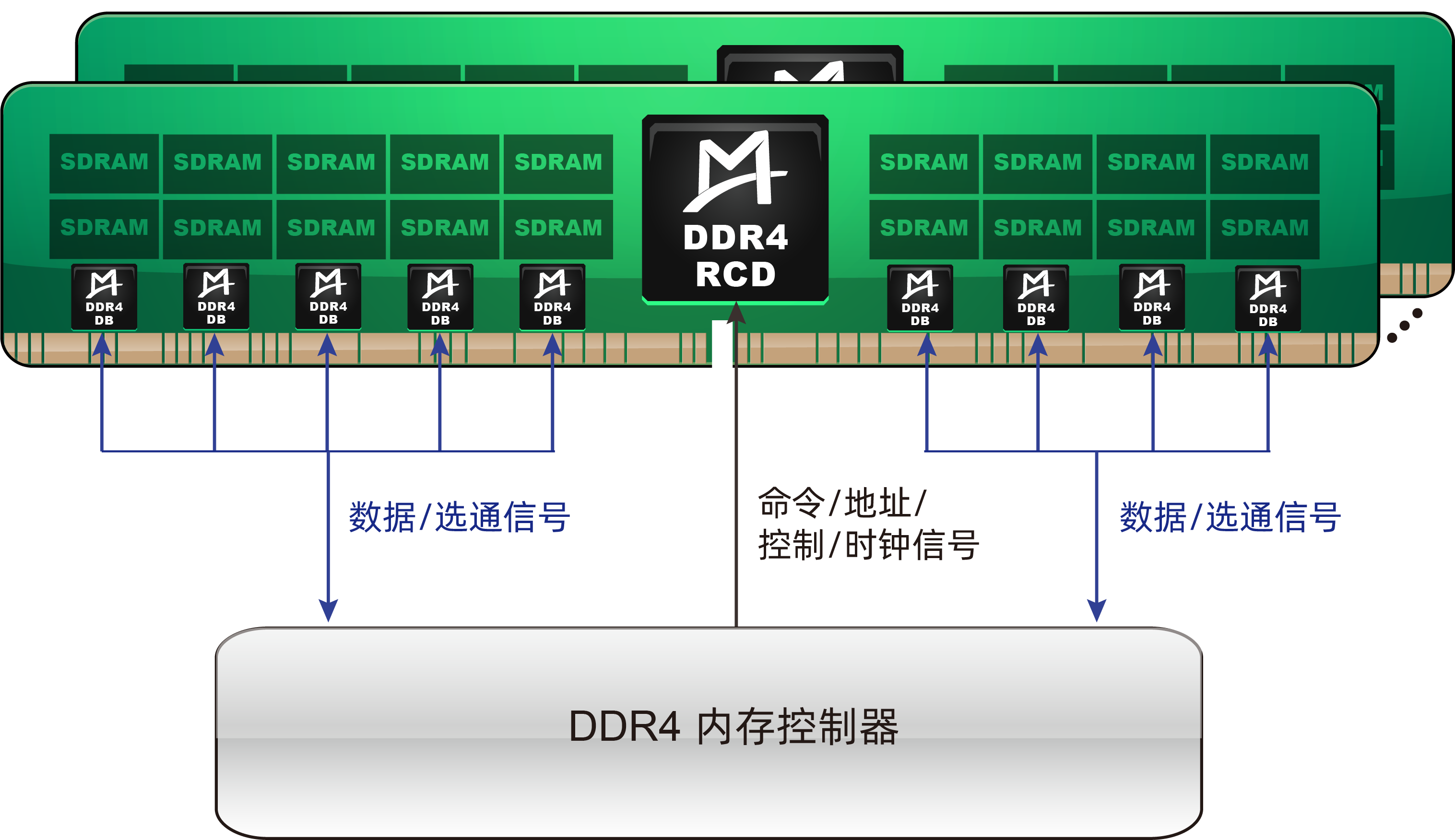

注:此处以 DDR4 LRDIMM 为例,展示了DB 芯片在内存模组上的应用示意图。

功能特点

- 符合JEDEC DDR4DB01标准

- 最高支持速率DDR4-2400

- 支持DDR4数据 (DQ) 信号双向重定时和1: 1再驱动

- 支持通过输入时钟重新生成数据控制 (DQS) 信号

- DQ通路内置FIFO,支持总线接口时域和DRAM接口时域解耦

- 支持最多四个pakcage rank

- 总线接口支持package rank定时校准

- 仅支持4位DRAM

- 内部生成VrefDQ,并可对总线接口和DRAM接口分开控制

- 支持1.2 V VDD电压

- BCOM接口支持奇偶校验错误和顺序错误检测

- DQ/MDQ输入输出特性可通过控制寄存器配置

- 输入时钟至输出DQ/MDQ的传输延迟恒定,不随电压和温度变化

- 支持Ron和IBT值的ZQ校准

- 支持同步ODT模式,包括RTT_PARK(以及RTT_NOM和RTT_WR)

- 支持多种DQ校准模式

- 支持PDA寻址 (Per-DRAM Addressability)

- 对于BCW写命令,支持PBA寻址 (Per-Buffer Addressability)

- 可编程Write和Read Preamble Time(1tCK模式和2tCK 模式)

- 总线接口支持Read Preamble训练功能

- 支持BCW读入模式和MPR读入覆盖模式

- 无复位引脚,芯片可在BCK_t 和 BCK_c都置低且BCKE置高时进入复位状态

- 输入时钟频率可变,支持双频环境切换

- 支持多种节电模式,如CKE低功耗模式、CK STOP模式等

- 支持Memory Bist和透明模式

- 绿色封装: FBGA (Fine-pitch Ball Grid Array)

典型应用

- DDR4 LRDIMM